台积电SoW技术突破,如何改变半导体产业的未来?

?在全球大模型火热与摩尔定律变缓的双重背景下(可以视为需求和技术曲线的超级剪刀差),台积电最近公布了其晶圆级计算(集成)技术的突破性进展和量产计划,也就是晶圆上系统(System on Wafer,SoW)。目前预计Sow会极大改变计算系统的发展进程,为大模型和未来的超级计算更大的算力支撑和扩展能力。SoW的量产预告也意味着工业界已经在紧锣密鼓的筹备超越传统GPGPU架构的新计算范式。

截至目前,只有 Cerebras 和特斯拉使用SoW技术开发了晶圆级芯片。这也是目前晶圆级设计和3D IC面临的艰巨挑战:相对晶圆芯片的出色性能和能效,设计和生产的复杂度明显更高,特别是需要解决面向热均衡和应力均衡的良率问题。这也意味着传统EDA的 "芯片设计->封装设计->封装"流程在3D IC设计领域失效。

在晶圆上系统集成工艺的研发取得突破性进展后,台积电确信,晶圆级设计的使用率不仅会大幅提升,而且人工智能和 HPC 等大趋势将需要更复杂的解决方案:垂直堆叠的晶圆系统设计。鉴于台积电能

01

晶圆上系统与3D IC

在晶圆上系统中,晶圆与附带组件(例如电源模组和冷却模组)组成一个完整的系统,而不仅仅是单个芯片。

晶圆上系统可以为设计者带来诸多好处,包括:

提高算力(提升单芯片晶体管数量)

减少数据中心占用空间

提高每瓦性能(能源效率)

本质上晶圆上系统变相将芯片面积扩大到整个晶圆(提升晶体管数量和算力),并且减少了芯片间互连的距离(减少互连功耗,减小互连线材占用的空间)。

台积电的晶圆片上系统简称为SoW,目标是为数据中心和大模型等人工智能应用颠覆性的性能提升。(需要注意SoW也是台积电的注册商标)

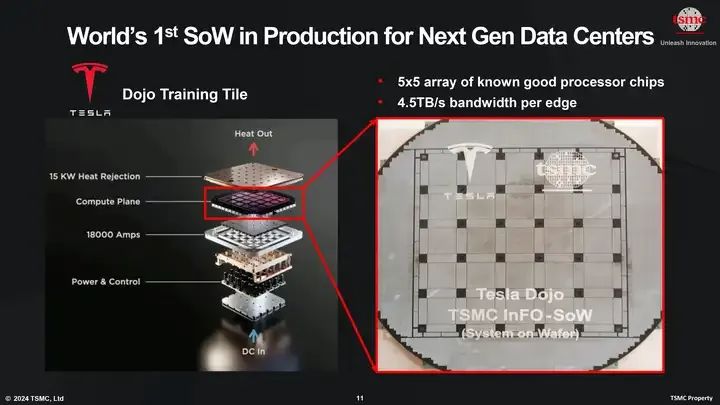

台积电目前的SoW方案包括 InFO-SoW 和CoW-SoW(注意官方说法并非CoWoS-SoW)。据说 InFO-SoW已经投入生产,客户大概是特斯拉。

在晶圆级系统中,逻辑晶圆平面是整个系统的地基。该晶圆设计需要充分考虑其结构层次、微架构、NoC、存储层次和编译框架。晶圆平面通过SoW集成技术进行互连。除了晶圆平面外,晶圆级系统还包括堆叠的存储芯片、散热器和供电单元。

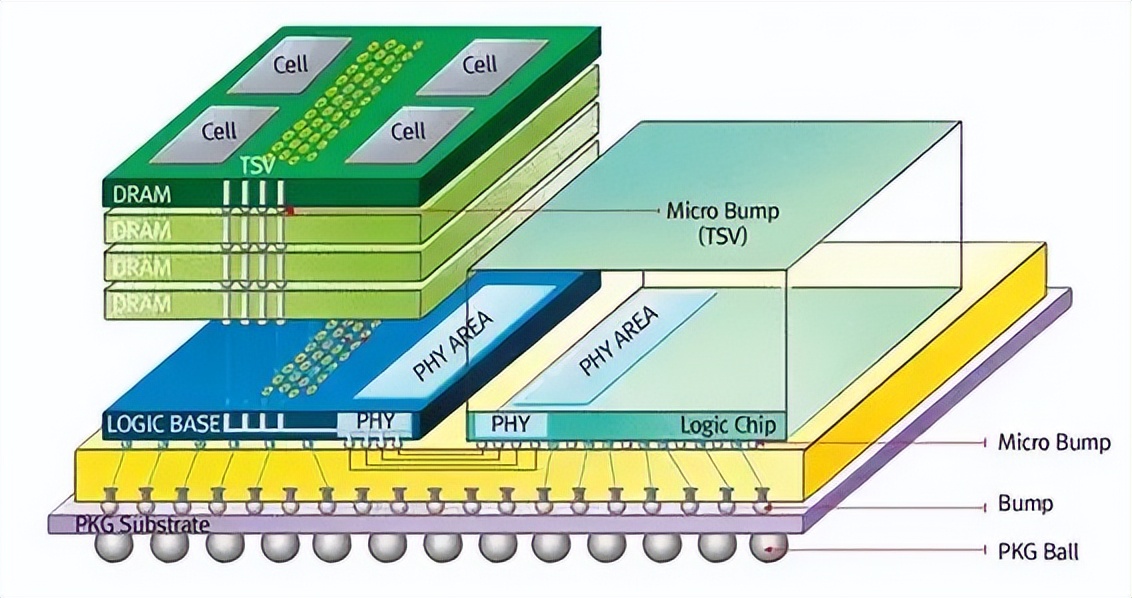

讲到SoW就不得不提到3D IC。3D IC即三维芯片,其概念与传统的平面IC工艺相对。例如比利时微电子研究中心(IMEC)提出的CMOS 2.0 ,将缓存和内存分成独立单元。然后以 3D 排列方式堆叠在逻辑芯片功能上。与AMD 的3D V-Cache(将 L3 内存堆叠在处理器顶部或下部)不太一样,IMEC则是垂直堆叠 L1、L2 和 L3 缓存。

但不管怎样的堆叠,本质上还是希望将逻辑与存储做的更近,以实现存算一体中的近存计算。

02

CoW-SoW

CoW即Chip on Wafer,属于台积电的SoIC工艺系列。

目前已有方案多使用 InFO-SoW 或其他晶圆级集成方法,处理器设计人员需要在逻辑Die上集成大量的SRAM来提升性能。但这对于下一代 AI 计算来说可能还不够。InFO-SoW也要求整个晶圆必须使用一种制造技术进行处理,难以进行不同工艺Die的集成,特别是难以集成Memory(包括SRAM和DRAM)工艺的Die。这样的不足就催生了CoW-SoW的出现。

按照台积电路线图,CoW-SoW将于 2027 年实现量产。该技术允许使用CoW(Chip on Wafer)方法在SoW顶部堆叠Memory或逻辑Die。按照目前业内流传的信息,最早量产的目标是将HBM4通过堆叠的方式与晶圆级处理器集成在一起。相对现有的2.5D封装方式,这种方法显然可以在逻辑芯片上集成容量大的多的HBM。(当年AMD选择HBM的原因,就是因为在CPU周边摆DDR容量上不去)

该技术与Info-SoW有相似之处,但显然使用CoW的方式可以获得更好的互连带宽,成本也会明显高于Info-SoW。

03

HBM4与HBM4E

HBM4和HBM4E显然是与CoW-SoW技术伴生的。

据称 SK 海力士计划在 2025 年下半年推出采用 12 层 DRAM 堆叠的首批 HBM4 产品,最早在 2026 年推出他们的 HBM4E 内存(带宽将是 HBM4 的 1.4 倍)。在海力士的HBM4和HBM4E方案中,HBM直接堆叠在逻辑Die上或下,互连距离缩短为芯片厚度,不再需要芯片宽度距离的平面连接。

美光则预计在 2026 年至 2027 年期间将有36GB 到 48GB 的 12-Hi 和 16-Hi 堆栈的HBM4推向市场。2028 年将推出 HBM4E,容量提高到每个堆栈 48GB 到 64GB。

04

Info-SoW

Info是集成扇出的缩写。相对与CoWoS,Info具有低成本的优势。

Tesla Dojo 的晶圆级处理器是基于台积电 InFO-SoW 技术量产的首款解决方案,与系统级封装 (SiP) 相比,具有低延迟高带宽、高性能、高带宽密度、供电电阻也更低。Dojo的每个训练模块由5x5的 D1芯片阵列排布而成,以二维Mesh结构互连。片上跨内核SRAM达到惊人的11GB,当然耗电量也达到了15kW的惊人指标。

当然Info-SoW结构上难以直接集成超大容量的HBM。我记得有人批评Groq 2019的方案中没有集成HBM,但实际上根本原因在于:想做到将对等需求的HBM集成,就只能将HBM堆叠逻辑Die的上或下,在当时并没有成熟的工艺Solution。

05

紧凑型通用光子引擎

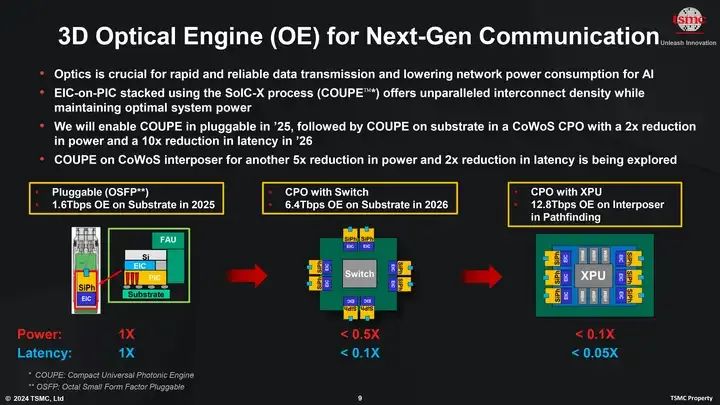

顺带提一下与CoW-SoW密切相关的光互连技术。SoIC-X 芯片堆叠技术将电芯片堆叠在光子芯片上 (EIC-on-PIC) ,在芯片间以较低的阻抗互连。通过SoIC-X技术引入硅光连接,可以获得更好的互连能效。

通过 COUPE可以提供高达 12.8 Tbps 的光学连接。预计COUPE第一代产品将于2025 年在可插拔 OSFP 设备中实验性推出,运行速度为1.6 Tbps,是当前铜缆以太网 (800 Gbps) 的两倍速度。第二代预计于2026 年推出,作为“共封装光学器件”(CPO)集成到 CoWoS 封装中,将硅光互连直接引入封装中速度将达到6.4 Tbps。COUPE 的第三代实现将直接集成到中介层(Interposer Layer)中,直接提供芯片级光互连,速度达到12.8 Tbps。

06

对半导体行业的影响

台积电SoW技术将推动的晶圆级计算技术的快速发展,预计对半导体行业会有极其影响深远的影响。传统的计算集群互连(通过光纤和交换机)将迅速集成为晶圆计算模式,桌面超算和桌面集群成为可能。

SoW技术在人工智能之外,也有非常广泛的应用空间,预计数据中心、高吞吐网络服务都会大批量采用SoW技术降低IDC成本。结合新的硅光互连集成技术,摩尔定律将进一步被延续,新的计算架构逐渐走入主流应用。

原文标题 : 台积电SoW技术突破,如何改变半导体产业的未来?

图片新闻

最新活动更多

-

7月30-31日报名参会>>> 全数会2025中国激光产业高质量发展峰会

-

7.30-8.1马上报名>>> 【展会】全数会 2025先进激光及工业光电展

-

免费参会立即报名>> 7月30日- 8月1日 2025全数会工业芯片与传感仪表展

-

精彩回顾立即查看>> 维度光电·引领光束质量分析应用全新浪潮【免费下载白皮书】

-

精彩回顾立即查看>> 2024(第五届)全球数字经济产业大会暨展览会

-

精彩回顾立即查看>> 【线下会议】全数会2024电子元器件展览会

推荐专题

分享

分享

发表评论

请输入评论内容...

请输入评论/评论长度6~500个字

暂无评论

暂无评论