ASML掀开台积电的老底,28纳米以后的芯片工艺升级都是假的!

近期光刻机龙头ASML突然发疯,发布PPT,揭开了台积电的等芯片制造企业的先进工艺的技术细节,指出台积电等的先进工艺,其实从28纳米以后就已脱离了原来的芯片工艺命名规则,芯片工艺的命名早已脱离了原来的命名规则。

ASML指出在28纳米以上工艺的时候,芯片制造工艺的栅极间距都低于芯片工艺的名字,即是65纳米,芯片的栅极间距低于65纳米,但是在28纳米以下工艺,芯片的栅极间距难以迅速缩短,芯片制造企业的命名已是脱离了这样的命名规则。

ASML表示3纳米工艺的栅极间距为23纳米,2纳米、1.4纳米工艺的栅极间距分别为22纳米、21纳米,预计1纳米的栅极间距为18纳米,甚至芯片制造企业可以根据这样的命名方式突破1纳米,0.2纳米工艺对应的栅极间距为12纳米左右。

专家就指出当下的硅基芯片极限工艺是1纳米,因为1纳米仅相当于2-3个硅原子的厚度,那样硅芯片可能会极为不稳定,电子容易击穿栅极,然而按照这种等效工艺命名规则,却可以出现出现0.1纳米的芯片制造工艺。

台积电的芯片工艺命名其实早在10纳米的时候就已被质疑,当时台积电研发出10纳米工艺的时候,高通就在内部指出10纳米工艺的性能提升有限,估计仅是与Intel的14纳米工艺相当,认为台积电夸大了10纳米工艺的性能,而后来10纳米工艺也是迅速被舍弃。

芯片工艺的命名规则发生改变,主要是由台积电和三星改变的,这两家芯片制造工艺认为自己的14/16纳米工艺上已追上了Intel,然而实际上他们的14/16纳米工艺其实比Intel的14纳米落后,三星的14纳米尤为落后,当时用三星的14纳米工艺生产的A9处理器就出现发热问题,而台积电的16纳米工艺生产的A9处理器性能更强、功耗更低。

但是台积电和三星此后不断升级工艺,芯片工艺性能相比自己的原有工艺提升20%-30%,已可以称为一代新工艺,同时如此也可以声称赶超Intel,再加上这两家芯片代工企业代表着最先进的水平,同时更先进的工艺又可以帮助芯片企业进行营销,于是各方就默认了台积电和三星的命名规则,当然到了后来的5纳米工艺之后,台积电和三星在芯片制造工艺方面确实超越了Intel。

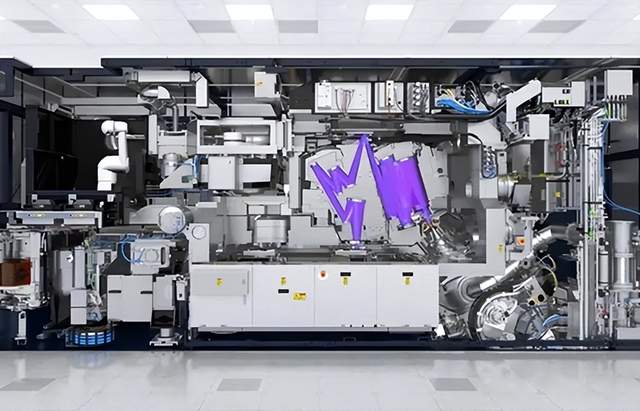

如今ASML突然翻出这回事,并对业界大肆宣传,也并非没有私心,此举或是为了给它研发下一代的光刻机进行营销造势。此前ASML曾宣称2纳米EUV光刻机将是最后一代光刻机,不过如今日本、美国在EUV光源方面已取得了一定的突破。

当前的2纳米EUV光刻机的EUV光纤为13.5纳米波长,这样的波长也说明当下的2纳米EUV光刻机生产的芯片栅极长度必然大于13.5纳米;日本和美国研发的新光源被命名为EUV-FEL,产生的光线波长将缩减到6.6-6.7纳米,可以进一步缩减芯片的栅极长度。

日本尼康、佳能和荷兰的ASML为全球仅剩的3家光刻机生产企业,日本希望重振光刻机产业,荷兰ASML则和美国深度捆绑,先进的EUV-FEL将引发日本和荷兰争夺光刻机产业,如此就可以延续他们的光刻机事业。

光刻机是一项很赚钱的生意,DUV光刻机只要数千万美元,第一代EUV光刻机售价1.2亿美元,2纳米EUV光刻机售价高达3.8万亿美元,这个市场如今就由佳能、尼康和ASML三家占有,谁先研发成功EUV-FEL,那么谁将成为下一代EUV光刻机的霸主,这也是ASML如此不顾台积电和三星的情面,而揭开芯片工艺真相的原因吧。

原文标题 : ASML掀开台积电的老底,28纳米以后的芯片工艺升级都是假的!

图片新闻

最新活动更多

-

4月30日立即报名>> 2026光学行业应用创新发展蓝皮书火热招编中!

-

即日-4.30立即下载>>> 【限时下载】《2025激光行业应用创新发展蓝皮书》

-

即日-5.31立即申报>>> 维科杯·OFweek 2026光学行业年度评选

-

5月31日立即申报>>> 维科杯•OFweek 2026激光行业年度评选

-

7月15-16日报名参会>>> OFweek 2026中国激光产业高质量发展峰会

-

精彩回顾立即查看>> 2026上海慕尼黑光博会维科网·VIP企业展台巡展直播

推荐专题

分享

分享

发表评论

登录

手机

验证码

手机/邮箱/用户名

密码

立即登录即可访问所有OFweek服务

还不是会员?免费注册

忘记密码其他方式

请输入评论内容...

请输入评论/评论长度6~500个字

暂无评论

暂无评论